电话:15301560529

新闻

News

等离子体刻蚀面临的挑战

点击量:949 日期:2023-08-21 编辑:硅时代

近几十年来,等离子刻蚀技术已取得了长足发展。利用等离子刻蚀技术,人们得以准确地雕刻器件结构,从而为晶体管尺寸的缩小以及性能的提升提供了保障。但是,当前的先进芯片关键尺寸更小,有些还具有三维结构(如FinFETs和3D NAND),这无疑对当前的等离子刻蚀技术提出了挑战。

均匀性一直是刻蚀工艺的一大考量。关键器件结构尺寸的允许工艺误差一般约为其自身尺寸的10%。例如,宽度为 10nm 的晶体管栅极结构,其允许误差仅为 1nm,相当于3至4个原子层。

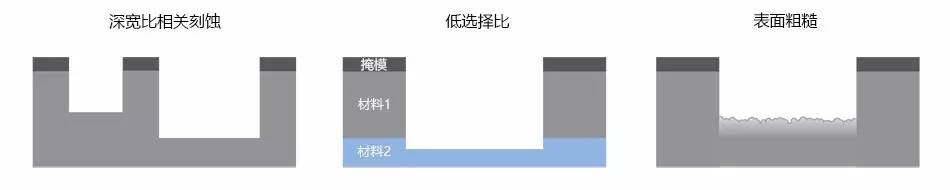

随着结构尺寸的不断缩小,人们需要尽可能地降低由各种原因导致的工艺误差。不同尺寸的结构在刻蚀中的速率差异是误差产生的重要原因之一。这种深宽比相关刻蚀(ARDE)会导致高深宽比结构的刻蚀速率要比低深宽比结构的刻蚀速率低。

另一项挑战则在于,刻蚀工艺需要在去除目标材料的同时,完好地保留下一层材料。

例如,一个薄膜堆栈由多层材料组成,我们可能只要去除最上面的那层(材料 1),而同时不能去除或损坏下层(材料 2)。材料 1 和材料 2 的刻蚀速率比称为“选择比”,很多刻蚀工艺都要求具有极高的选择比。

第三项挑战在于,当达到期望的深度之后,等离子体中的高能离子可能会导致硅片表面粗糙或底层损伤,这是需要极力避免的问题。对于最先进的芯片,工程师们需要对上述参数进行更严格的控制,以期获得原子级高保真度。

公安备案号:苏公网安备32059002006658号

公安备案号:苏公网安备32059002006658号

微特云办公系统 微纳制造 MEMS设计

微特云办公系统 微纳制造 MEMS设计