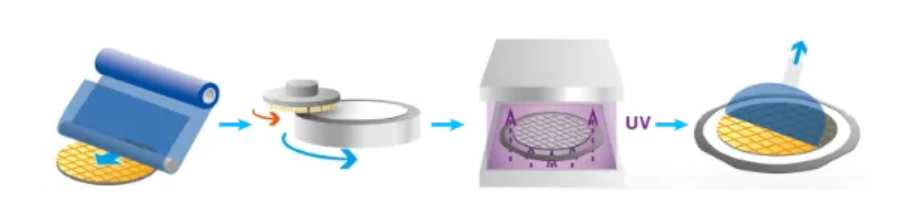

背金,又称背面金属化,通过在晶圆背面镀上金属层,不仅增强了芯片的热传导能力,还优化了焊接性能,为高性能计算芯片的稳定运行提供了坚实保障。本文将深入探讨背金工艺中的核心要素——钛(Ti)黏附层及其在多层金属体系中的应用,同时解析背金工艺的流程与质量控制标准。钛(Ti)在半导体封装领域,特别是作为背金工艺的黏附层,展现出了卓越的性能。其与硅(Si)及碳化硅(SiC)等半导体材料能形成稳定的化合物,具备良好的结合力。对于SiC这一硬度高、化学稳定性强的材料,Ti虽可能略逊于与Si的结合力,但差异并不显著,足以满足大多数应用需求。评估背金层质量的关键指标在于剥离强度与脱落比例。剥离强度衡量了金属层与硅片背面的粘附性,而脱落比例则直接反映了镀层在加工或使用过程中脱落的风险。根据行业实践,单个芯片镀层脱落比例超过10%,或整个圆片镀层脱落比例超过5%,均被视为不良品。这些严格的质量控制标准,确保了半导体产品的可靠性和长期稳定性。背金工艺中的金属层通常由三层组成:黏附层、阻挡层和防氧化层。Ti作为常见的黏附层材料,不仅与Si片背面结合紧密,还能有效降低欧姆接触的阻值。然而,根据不同的应用场景,如MOSFET和IGBT等功率器件,背金体系也会有所调整。MOSFET背金体系:通常采用Ti/NiV/Ag组合。Ti作为黏附层,NiV作为阻挡层防止金属扩散,Ag作为防氧化层覆盖在晶圆表面,防止Ni的氧化。各层厚度根据具体需求调整,如Ti层厚度一般在20-200nm之间,NiV层在200-400nm,Ag层则在100-2000nm。IGBT背金体系:可能采用Al/Ti/NiV/Ag组合。Al作为第一层,主要考虑到其与Si的良好结合力及较低的成本;后续层的作用与MOSFET体系相似,分别承担黏附、阻挡和防氧化的功能。背金工艺的作用主要体现在三个方面:一是形成理想的欧姆接触,降低接触电阻;二是增强芯片的散热能力,确保高性能计算芯片的稳定运行;三是提升焊接性能,便于芯片的封装与互连。背金工艺的典型流程包括贴胶纸保护晶圆正面、减薄硅片背面、硅刻蚀消除缺陷与应力、清洁处理确保金属层与Si的结合力、以及背面金属化沉积相应的金属层。每一步都至关重要,直接影响最终产品的质量与性能。1.贴胶纸:保护晶圆正面的图形不受后续加工步骤的影响。2.减薄:采用机械抛光方法,将硅片背面研磨至适宜厚度,以适应封装需求。3.硅刻蚀:使用硝酸和氢氟酸混合溶液进行刻蚀,消除内部应力,增大表面粗糙度,便于金属沉积。4.清洁处理:用BOE(缓冲氧化刻蚀液)洗去硅表面的自然氧化层,确保金属层与Si的良好结合。5.背面金属化:采用电子束蒸发或磁控溅射方法,沉积Ti/Ni/Au(或Ag)等多层金属体系。各层厚度需根据具体应用场景精心设计。面对日益增长的芯片性能与可靠性需求,优化背金工艺成为业界关注的焦点。通过改进背面粗糙化工艺、优化金属蒸镀参数、以及引入新型材料与技术,可以显著提升背面金属层的粘附性与整体性能。同时,严格控制加工过程中的环境条件、原材料质量及工艺参数,也是确保背金工艺稳定可靠的关键。

公安备案号:苏公网安备32059002006658号

公安备案号:苏公网安备32059002006658号

微特云办公系统 微纳制造 MEMS设计

微特云办公系统 微纳制造 MEMS设计