新闻

News

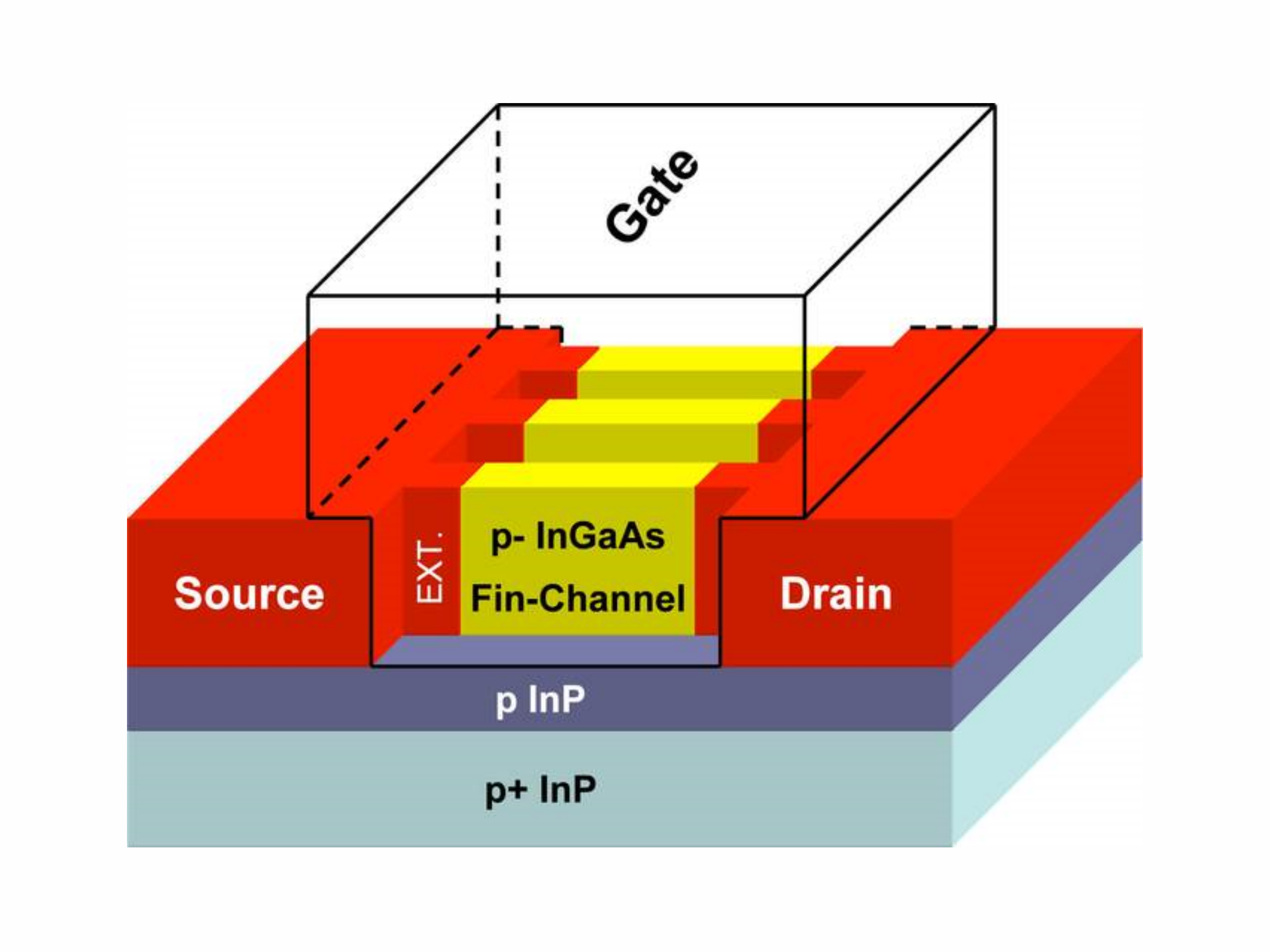

FinFET工艺制造流程详解

点击量:5666 日期:2025-05-23 编辑:硅时代

FinFET的制造流程与传统平面CMOS工艺存在显著差异,核心在于三维Fin结构的形成与高精度工艺控制。以下以主流的Bulk FinFET工艺为例,结合5nm及以下先进节点的技术演进,详细拆解关键步骤及技术细节:

1. 衬底准备与初始结构

衬底选择:采用轻掺杂p型硅(电阻率1-10 Ω·cm),或应变硅(SSOI)以提升迁移率。

缓冲层生长:通过热氧化生成1-2nm SiO₂界面层,降低后续刻蚀对硅衬底的损伤。

硬掩模沉积:

材料选择:双层堆叠结构(如SiO₂/SiNx,厚度20nm/50nm),用于后续Fin图案转移。

沉积工艺:低压化学气相沉积(LPCVD)确保膜厚均匀性(±1%)。

2. Fin结构成形

(关键技术:多重图形化与高深宽比刻蚀)

光刻与SADP/SAQP:

光刻胶涂布:采用旋涂工艺形成厚度80-100nm的光刻胶(如ArF光刻胶,分辨率≤40nm)。

双重/四重图形化:

SADP(自对准双重曝光):用于16nm-10nm节点,Fin pitch 45-30nm。

SAQP(自对准四重曝光):用于7nm及以下节点,Fin pitch缩至20-14nm(需结合EUV光刻优化)。

侧墙形成:通过原子层沉积(ALD)生成SiN侧墙(厚度5-10nm),确保线宽一致性(CDU≤1nm)。

Fin刻蚀:

干法刻蚀工艺:

Bosch工艺:交替进行SF₆刻蚀与C₄F₈钝化,实现高深宽比(HAR>5:1)Fin结构。

关键参数:Fin高度30-60nm(3nm节点达60nm),宽度5-8nm,侧壁角度>88°。

损伤控制:采用低温刻蚀(-20℃)减少硅晶格损伤,表面粗糙度(RMS)<0.3nm。

Fin形貌优化:

湿法清洗:使用稀释HF(DHF)去除刻蚀残留物,避免Fin根部缺陷。

退火处理:快速热退火(RTA,1050℃/1s)修复刻蚀引起的晶格损伤。

3. 阱区与隔离结构(STI)

阱注入(Well Implantation):

先阱工艺:在Fin成形前完成阱区注入(如B⁺注入p-well,剂量1e13 cm⁻²,能量30keV)。

后阱工艺:通过离子注入掩模(如SiON硬掩模)选择性注入,确保阱区与Fin对准精度(±2nm)。

浅槽隔离(STI):

高密度等离子体氧化(HDP-CVD):沉积SiO₂填充Fin间隙,避免空洞(Void-Free填充要求间隙<10nm)。

化学机械抛光(CMP):采用SiO₂抛光液(pH=10-11),Fin高度均匀性控制在±1nm以内。

回刻工艺(Etch Back):干法刻蚀调整STI高度,暴露Fin顶部(保留Fin高度70%-80%)。

4. 栅极工程(后栅工艺,Gate-Last)

(核心挑战:高κ介质与金属栅集成)

假栅(Dummy Gate)形成:

多晶硅沉积:LPCVD沉积非晶硅(厚度50-80nm),经退火晶化为多晶硅。

栅极图案化:EUV光刻(13.5nm波长)定义栅长(Lg=12-16nm@5nm节点),线宽粗糙度(LWR)<1.5nm。

源漏外延(Epitaxy):

选择性外延生长(SEG):

PMOS:嵌入SiGe(Ge含量25%-40%),引入单轴压应力,空穴迁移率提升50%。

NMOS:嵌入SiC(C含量1%-2%)或SiP,引入拉应力,电子迁移率提升30%。

原位掺杂:B(PMOS)或As(NMOS),浓度1e20-5e20 cm⁻³,降低接触电阻。

高κ金属栅(HKMG)集成:

假栅移除:

干法刻蚀:Cl₂/HBr等离子体刻蚀多晶硅,选择性>100:1(避免损伤Fin)。

界面层处理:采用臭氧氧化生成0.5-1nm SiO₂界面层(等效氧化物厚度EOT≈0.3nm)。

高κ介质沉积:

ALD HfO₂:厚度2-3nm(k≈25),漏电流较SiO₂降低3个量级(<1e-3 A/cm²@1V)。

界面优化:氮等离子体处理(N₂/H₂,400℃)降低氧空位密度至<1e11 cm⁻²。

金属栅堆叠:

功函数层(WFM):TiN(PMOS,WF≈4.7eV)与TiAlC(NMOS,WF≈4.2eV)双金属层。

填充金属:ALD W或Co(电阻率<10μΩ·cm),避免空隙(Void-Free填充)。

5. 互连与后端工艺(BEOL)

接触孔(Contact)形成:

自对准硅化物(Salicide):NiPt合金(厚度10nm),退火形成低阻NiSi(Rc<20Ω·μm)。

双重大马士革工艺:

介电层:超低k材料(如SiCOH,k=2.4-2.7)降低寄生电容。

金属填充:物理气相沉积(PVD)TaN/Ta扩散阻挡层+Cu电镀(5nm节点引入Co互连)。

多层金属化(10-15层):

EUV光刻:定义最小金属节距(MP=28nm@5nm节点),通孔直径<20nm。

气隙(Air Gap)技术:在密集布线区引入空气介电(k≈1),电容降低30%。

6. 先进工艺演进(3nm及以下节点)

Fin结构优化:

Super Fin(Intel):鳍高增至70nm,侧壁曲率优化,驱动电流提升18%。

Forksheet FET(imec):N/P MOS Fin由介电墙隔离,标准单元面积缩减20%。

环栅(GAA)过渡:

纳米片(Nanosheet):台积电N3工艺,堆叠3-4层Si纳米片(厚度5nm),栅极全环绕。

CFET(互补FET):垂直堆叠NMOS与PMOS,逻辑单元密度翻倍。

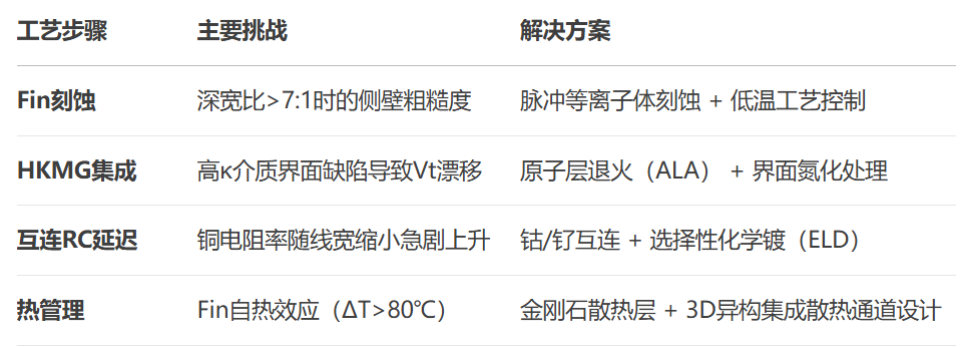

工艺挑战与解决方案

FinFET工艺的制造流程高度依赖先进光刻、原子级沉积/刻蚀与材料创新。从Fin成形到GAA结构的演进,技术节点每推进一代,需突破至少3项关键工艺瓶颈(如EUV套刻精度、原子级掺杂控制等)。未来,FinFET将与GAA纳米片协同,持续推动摩尔定律至1nm以下时代。

公安备案号:苏公网安备32059002006658号

公安备案号:苏公网安备32059002006658号

微特云办公系统 微纳制造 MEMS设计

微特云办公系统 微纳制造 MEMS设计